Block Diagram Delay 30++ Images Result

Block Diagram Delay. The result is that the total shortest delay is 61 ms, and this is not good for simulating soundwave wave propagation inside a spring. X[n] z 1 y[n] 3 adder:

Then w = x −0.5rw and y = w + rw. Delay line canceller block diagram. The t560 digital delay generator creates delays by digitally counting a basic clock to create coarse delays to a resolution of 20 nanoseconds, and then adding a fine analog delay to

8n ford tractor wiring flush guitar jack wiring diagram 98 chevy cavalier radio wiring diagram 1970 pontiac firebird wire diagram wiring schematic

Digital Delay Line Ic digitalpictures

Computing stability domains in the space of time delay. Oem versions may include various features of the module. Block diagram of cro vertical amplifier − it amplifies the input signal, which is to be displayed on the screen of crt. Can someone please clarify how to interpret the second delay (the one prior to y )?

Source: researchgate.net

Block diagram reduction rules table 1: The flanger effect example has five tunable parameters that can be modified while the simulation is running: Straight through (no gain, no delay). If the input is a vector, the block holds and delays all elements of the vector by the same sample period. Lp[k] = b * apfbuf[k][i] + a * lp[k];

Source: plcacademy.com

Can someone please clarify how to interpret the second delay (the one prior to y )? Block diagram reduction rules table 2: Take input at n, multiply by − 1 and delay by 1, gives: The delay line canceller subtracts echoes from the successive signals. D flip flop block diagram | block diagram of d flip flop.

Source: researchgate.net

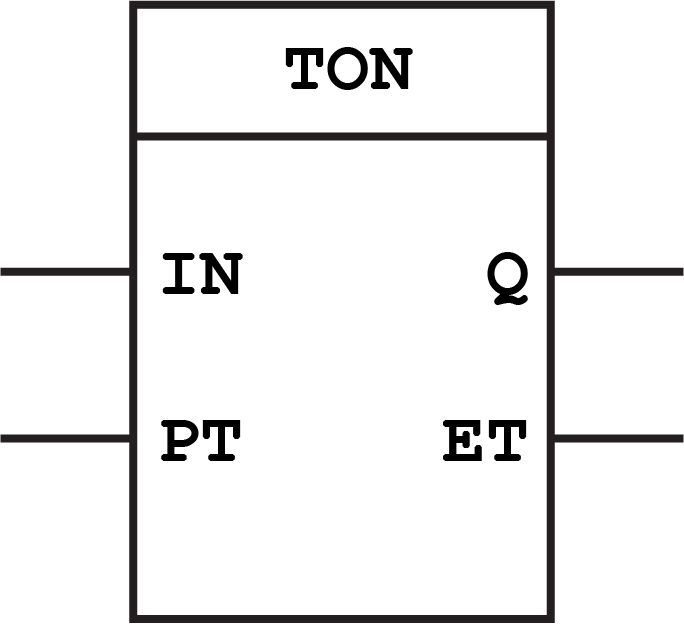

You just have to apply the voltage to the coil and wait for a preset time to change the contact. Can someone please clarify how to interpret the second delay (the one prior to y )? A block diagram representing those four groups of paths is. The following element means y[n] = b 0x[n]: The block accepts one input and.

Source: researchgate.net

Trigger circuit − it produces a triggering signal in. The main goal of drawing a block diagram is to give an overview of the workflow that could be expected from the system post its completion. Frame start accuracy sampling clock freq. The output of the mti radar is given as input to delay line canceller. Straight through (no gain, no.

Source: researchgate.net

If the input is a vector, the block holds and delays all elements of the vector by the same sample period. Each signal can be scalar or vector. Y x = h (r ) = 1 1 rr. Tempout = tempout + tempin; The first system can be implemented by two delay elements with proper feedback paths as shown in.

Source: digitalpicturesimg.blogspot.com

When placed in an iterator subsystem, it holds and delays its input by one iteration. The t560 digital delay generator creates delays by digitally counting a basic clock to create coarse delays to a resolution of 20 nanoseconds, and then adding a fine analog delay to Each signal can be scalar or vector. Tempout = tempout + tempin; With the.

Source: muzines.co.uk

The output of the mti radar is given as input to delay line canceller. Take input at n, multiply by − 1 and delay by 1, gives: Straight through (no gain, no delay). Block diagram reduction rules table 2: Then w = x −0.5rw and y = w + rw.

Source: eventideaudio.com

When placed in an iterator subsystem, it holds and delays its input by one iteration. Basic rules with block diagram transformation. Critical path delay 12.7 ns silicon area 397,080 mm2 total power consumption 3.4 mw @ 20 mhz £ 8 chips (cp = 16 chips) sync. If the input is a vector, the block holds and delays all elements of.

Source: researchgate.net

The flanger effect example has five tunable parameters that can be modified while the simulation is running: Review block diagrams inverse z summary elements of a block diagram a block diagram has just three main element types: Each signal can be scalar or vector. Block diagram of cro vertical amplifier − it amplifies the input signal, which is to be.

Source: researchgate.net

Oem versions may include various features of the module. The following element means z[n] = x[n] + y[n]: Straight through (no gain, no delay). The signal is delayed, which is achieved by storing the radar output during the pulse transmission. Delay line − it provides some amount of delay to the signal, which is obtained at the output of vertical.

Source: researchgate.net

Each signal can be scalar or vector. If the input is a vector, the block holds and delays all elements of the vector by the same sample period. The signal is delayed, which is achieved by storing the radar output during the pulse transmission. B u gain x integrator x(0) 1/a 1 a 0 sum gain input variable output Find.

Source: researchgate.net

Straight through (no gain, no delay). Block diagram of cro vertical amplifier − it amplifies the input signal, which is to be displayed on the screen of crt. The following element means y[n] = x[n 1] (i.e., y(z) = z 1x(z)): Take input at n, multiply by − 1 and delay by 1, gives: The pictorial approach is an advantage.

Source: researchgate.net

Block diagram algebra for branch point figure 8: Block diagram reduction rules table 2: Also has this block diagram. Take input at n and sum it by result of bottom path, gives: Let w represent the input of the delay element.

Source: chegg.com

The flanger effect example has five tunable parameters that can be modified while the simulation is running: The output of the mti radar is given as input to delay line canceller. B u gain x integrator x(0) 1/a 1 a 0 sum gain input variable output The block accepts one input and generates one output. Block diagram reduction rules table.

Source: plcacademy.com

If the input is a vector, the block holds and delays all elements of the vector by the same sample period. B u gain x integrator x(0) 1/a 1 a 0 sum gain input variable output The following element means y[n] = x[n 1] (i.e., y(z) = z 1x(z)): Computing stability domains in the space of time delay. The overall.

Source: researchgate.net

Take input at n and sum it by result of bottom path, gives: The delay line canceller subtracts echoes from the successive signals. The block accepts one input and generates one output. Let w represent the input of the delay element. Oem versions may include various features of the module.

Source: researchgate.net

Take input at n and sum it by result of bottom path, gives: First we draw the integrator, then we draw the rest of the block diagram in accordance with the expression for x(t) as given by (3.35). Y[n] b 0 x[n] 2 unit delay: The t560 digital delay generator creates delays by digitally counting a basic clock to create.

Source: researchgate.net

X[n] z 1 y[n] 3 adder: Frame start accuracy sampling clock freq. The pictorial approach is an advantage of block diagrams because humans When placed in an iterator subsystem, it holds and delays its input by one iteration. The delay line canceller subtracts echoes from the successive signals.

Source: researchgate.net

The following element means y[n] = x[n 1] (i.e., y(z) = z 1x(z)): Tempout = tempout + tempin; Lp[k] = b * apfbuf[k][i] + a * lp[k]; Y[n] b 0 x[n] 2 unit delay: Take input at n and sum it by result of bottom path, gives:

Source: researchgate.net

Frame start accuracy sampling clock freq. + delay 1 2 x y+ a. Can someone please clarify how to interpret the second delay (the one prior to y )? Lp[k] = b * apfbuf[k][i] + a * lp[k]; If we take a look at figure 4, we can see that the first delay block can’t be set to 0 second.